verilog - I'm designing a mod-3 asynchronous counter. The circuit is expected to count from 0 to 2 and the flip flops are set as soon as q become 3 - Electrical Engineering Stack Exchange

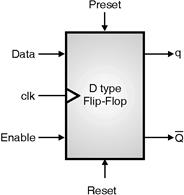

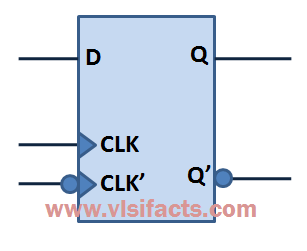

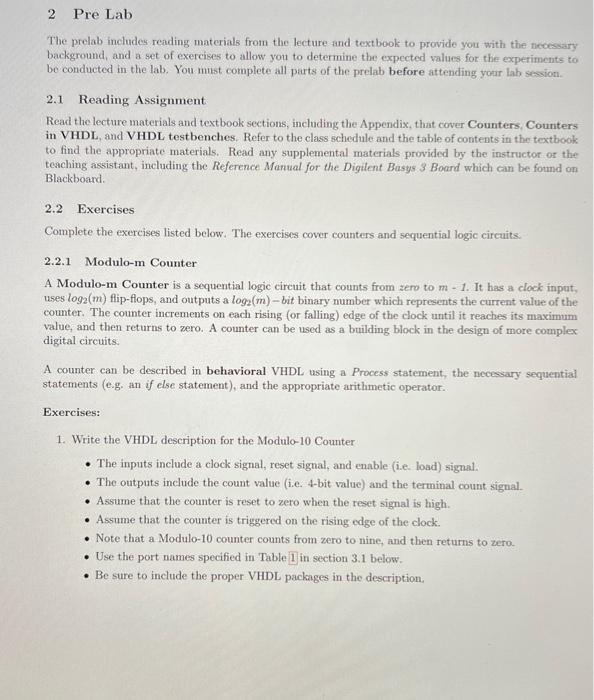

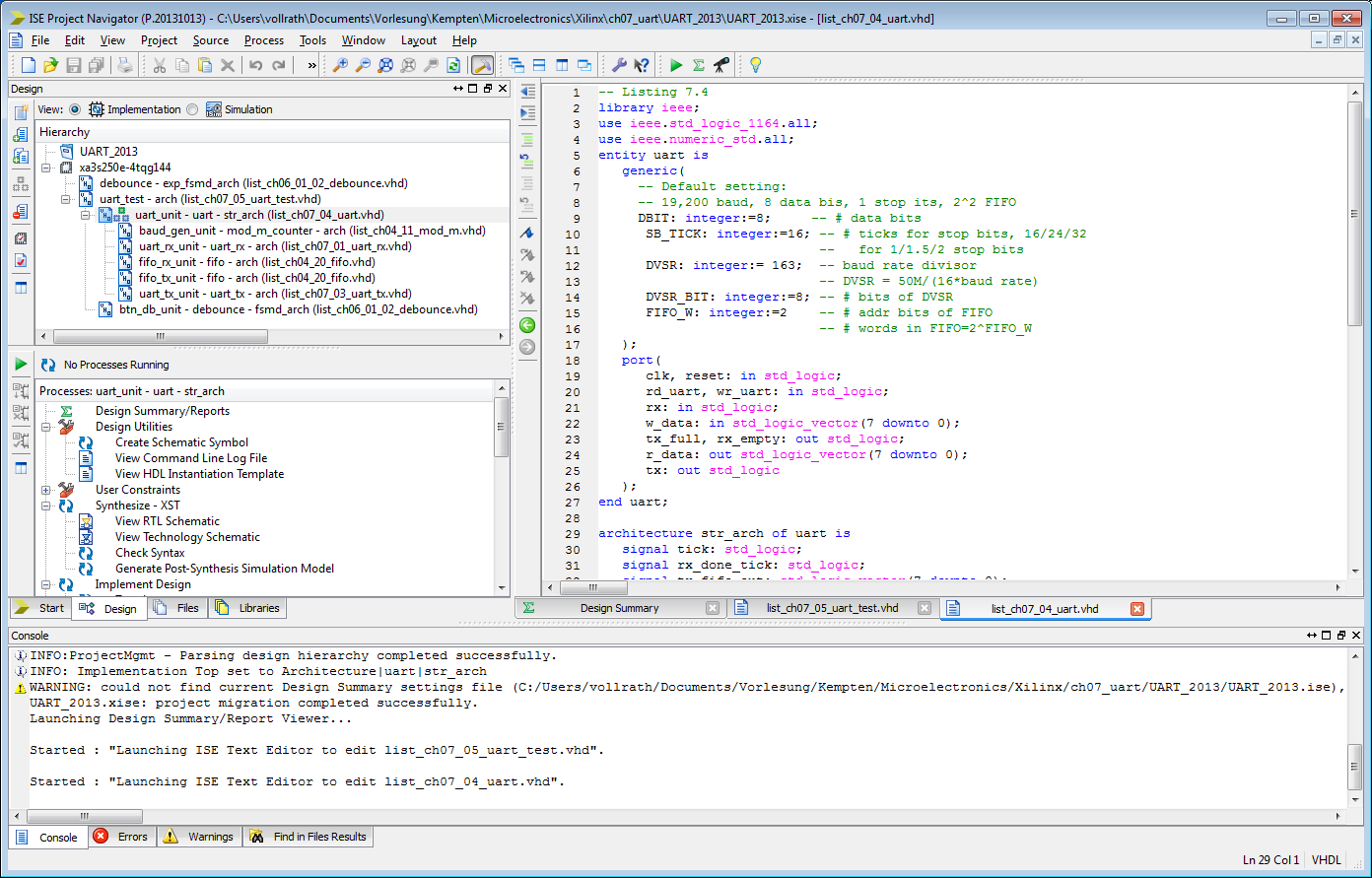

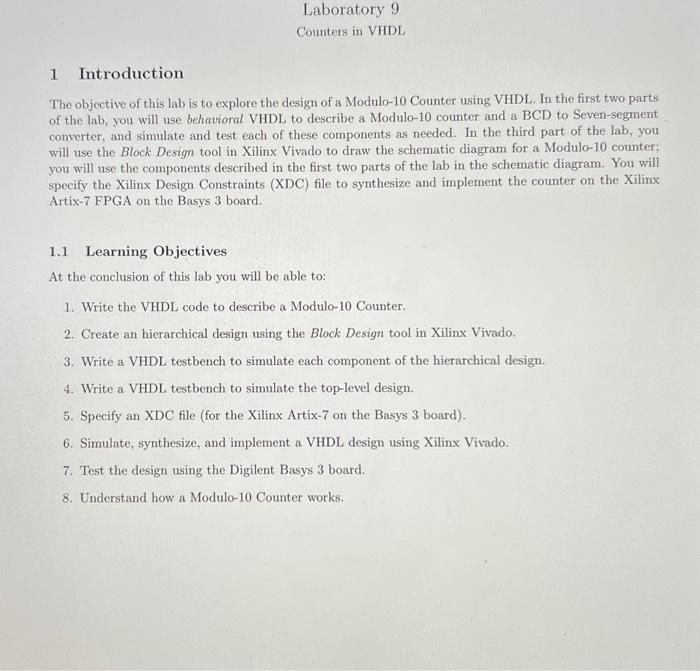

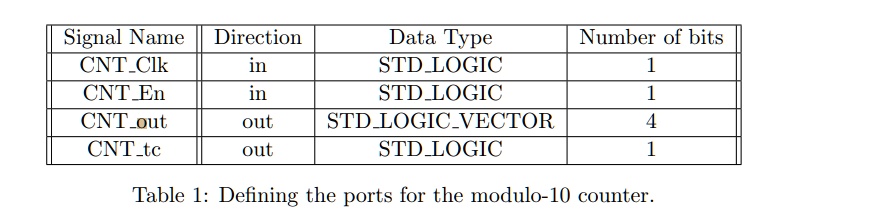

SOLVED: Write the VHDL description for the Modulo-10 Counter • The inputs include a clock signal, reset signal, and enable (i.e. load) signal. • The outputs include the count value (i.e. 4-bit

SOLVED: (TCO 5) Determine the period for the most significant bit for a counter circuit that contains 12 flip-flops with an input clock frequency of 20.48 MHz. The counter is not truncated. (

lesson 34 Up Down Counter Synchronous Circuit using D Flip Flops in VHDL with and with reset input - YouTube

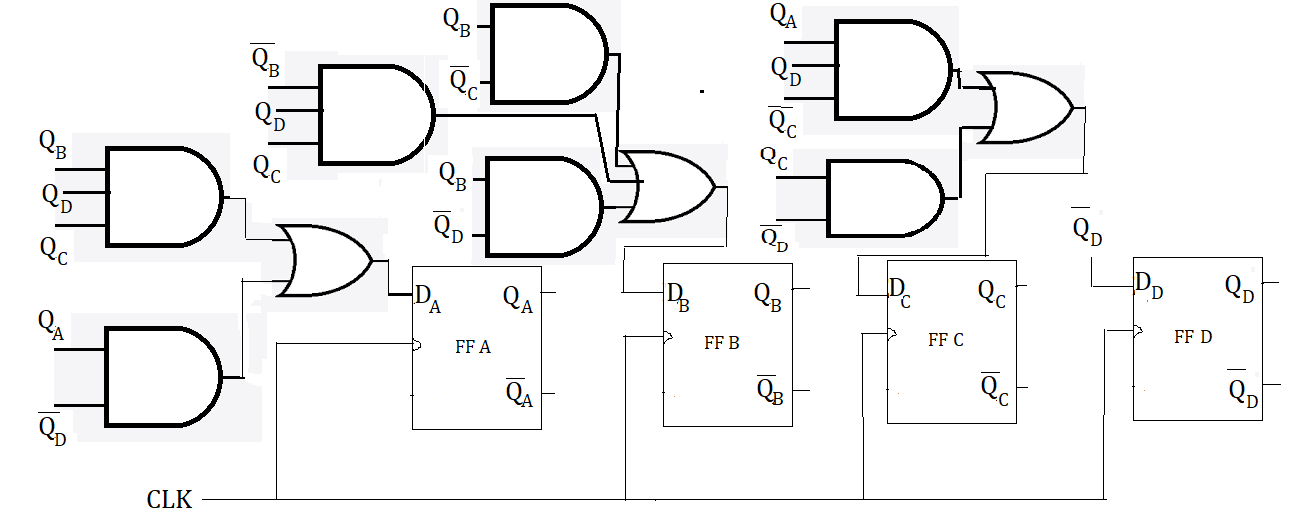

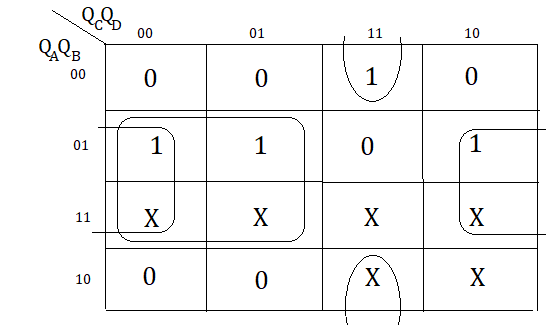

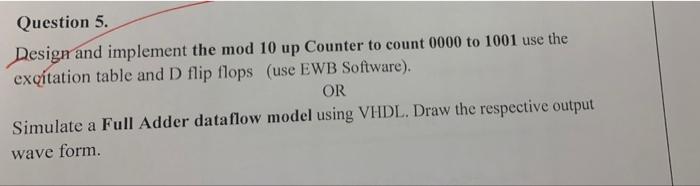

Design mod-10 synchronous counter using JK Flip Flops.Check for the lock out condition.If so,how the lock-out condition can be avoided? Draw the neat state diagram and circuit diagram with Flip Flops.

SOLVED: Write the VHDL description for the Modulo-10 Counter • The inputs include a clock signal, reset signal, and enable (i.e. load) signal. • The outputs include the count value (i.e. 4-bit

lesson 34 Up Down Counter Synchronous Circuit using D Flip Flops in VHDL with and with reset input - YouTube